# A Simplified Microwave Model of the GaAs Dual-Gate MESFET

JAMES R. SCOTT, STUDENT MEMBER, IEEE, AND ROBERT A. MINASIAN, MEMBER, IEEE

**Abstract** — A simplified wide-band model of the GaAs dual-gate MESFET based upon the familiar cascode representation is presented, which is valid over the frequency range of 2–11 GHz. The equivalent circuit contains 14 elements and the parameter values are directly determined from 3-port  $S$ -parameters over the frequency range of 4–6 GHz, and dc data. Separate microwave measurements of each FET part are not required, thus greatly reducing the number of measurements required to fully characterize the device. The method has been used to model a GaAs dual-gate MESFET in which both FET parts were in the saturation region, and good agreement has been obtained between measured and calculated results without the need for computer optimization.

## I. INTRODUCTION

THE DUAL-GATE GaAs MESFET has found application in a wide range of signal processing circuits. This is due to its inherent versatile functional capability as a device with two control gates, coupled with enhanced isolation characteristics. Circuit applications of dual-gate MESFET's include frequency converters and multipliers [1], [2], modulators [3], pulse regenerators [4], phase shifters [5], and variable gain amplifiers [6].

Being a four-terminal device, however, causes additional complexity in the modeling procedure, and this has hampered the design and analysis of dual-gate FET circuits. The basic device model is constructed from a cascode connection of two single-gate FET's. Initial modeling techniques utilized approximate analytical expressions to determine the element values in the equivalent circuit [7], [8]; however, this leads to limited accuracy and frequency range of validity, especially if the assumption of equal FET parts is made [9].

A more accurate modeling method has been reported recently by Tsironis and Meierer [10]. This utilizes dc and microwave measurements to characterize each FET part separately under its actual bias conditions. Though the method is quite general, it involves 28 circuit elements and requires several sequential steps for evaluation. At a given device bias point, two sets of two-port  $S$ -parameters need to be measured at two different auxiliary bias conditions, as well as the three-port  $S$ -parameters of the device over a broad frequency range. In addition, a total of four levels of computer optimization are required to define the model elements, making the entire procedure very lengthy. A refinement of this technique was reported by Ashoka and

Manuscript received June 13, 1983; revised Dec. 15, 1983. This work was supported in part by the Australian Radio Research Board.

The authors are with the Electrical Engineering Department, University of Melbourne, Parkville, Victoria, Australia 3052.

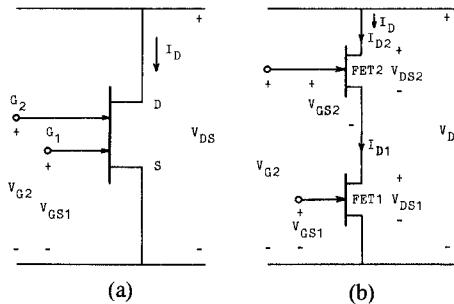

Fig. 1. (a) Dual-gate MESFET. (b) Decomposition into an equivalent cascode connection of two single-gate MESFET's.

Tucker [11], although the method basically employed similar principles.

The purpose of this paper is to present a new simple and efficient modeling procedure for the dual-gate MESFET. The active device model contains 14 elements and is derived from a design-oriented equivalent circuit developed previously for single-gate MESFET's [12]. The dual-gate FET characterization is extremely efficient and rapid since it only requires some dc data and three-port  $S$ -parameter measurements at a few frequencies, and utilizes simple analytical relations, yet the model applies with good accuracy over a wide frequency range.

The simplified device model is presented in Section II. Section III describes the parameter acquisition technique for determining the model elements, and relevant three-port parameter transformations are given in the Appendix. The model accuracy is evaluated in Section IV, which presents a comparison between predictions and measured microwave parameters on an actual dual-gate FET.

## II. SIMPLIFIED CIRCUIT MODEL

The dual-gate MESFET representation as a cascode connection of two single-gate FET parts [3], [7], [8] is depicted in Fig. 1. The equivalent circuit is deduced by combining two single-gate FET models [7], [8], [10]; however, the resulting equivalent circuit tends to be too complex for design and for parameter acquisition.

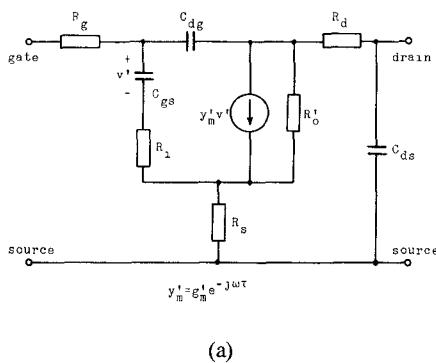

In order to obtain a more tractable representation, a simplified model was established for the device, and efficient analytical techniques for parameter evaluation were developed. Previous work by one of the authors [12] has shown that the conventional single-gate FET model shown in Fig. 2(a) may be reduced to the simplified form of Fig. 2(b) with little loss of accuracy for frequencies up to

Fig. 2. Single-gate MESFET models. (a) Conventional model. (b) Simplified model (after Minasian [12]).

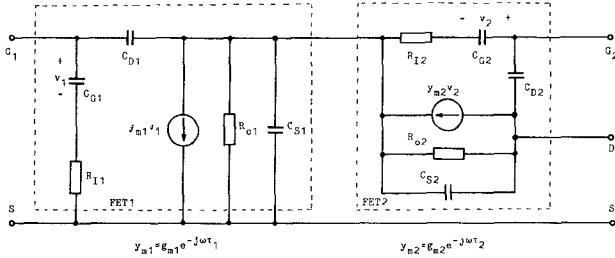

Fig. 3. Simplified dual-gate MESFET equivalent circuit.

12 GHz. The simplified circuit also has the advantage that all the element values may be determined directly from microwave measurements. The application of these constituent FET models to obtain a circuit model for the dual-gate FET is shown in Fig. 3, where the terminals refer to the active device terminals. The model contains 14 elements and represents a substantial simplification compared to previous dual-gate FET models.

To test the validity of the new simplified dual-gate MESFET model, three-port  $S$ -parameters referenced to the active device terminals were calculated over the frequency range of 2–11 GHz for the simplified model of Fig. 3 and the more detailed model of Tsironis and Meierer [10]. The element values for the full model were those of Tsironis and Meierer's FET(a), while the corresponding element values for the simplified model were derived from those of the full model using [12, eq. (14)–(19)]. It was found that the magnitudes of all the nine  $S$ -parameters were within 4 percent of those of the full model, and the phase discrepancy of all the  $S$ -parameters was less than 3 degrees over the entire 2–11-GHz range. This verifies the excellent accuracy of the dual-gate FET model of Fig. 3 compared to

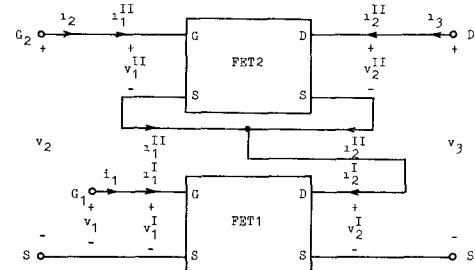

Fig. 4. Cascode connection of two two-port networks (FET1 and FET2) to form a three-port network.

more detailed models, while at the same time enabling a substantially simplified representation.

### III. DETERMINATION OF MODEL ELEMENTS

One of the principal aims of the modeling procedure was to arrive at a rapid and efficient parameter acquisition technique. The analytical basis for the expressions used for element evaluation is now described.

#### A. FET1 Model Elements

If FET1 and FET2 are represented by their two-port  $z$ -parameters  $[Z^I]$  and  $[Z^{II}]$ , respectively, the dual-gate MESFET may be represented as a cascode connection of two two-port networks as shown in Fig. 4, resulting in a three-port network, with port voltages and currents as defined in Fig. 4. Taking port 1 as being between gate 1 and the source, port 2 as being between gate 2 and the source, and port 3 as being between the drain and the source, the cascode connection forces the following relationships between the three-port terminal voltages and currents and the terminal voltages and currents on the constituent two-port networks (FET1 and FET2):

$$v_1 = v_1^I \quad (1)$$

$$v_2 = v_2^I + v_1^II \quad (2)$$

$$v_3 = v_2^I + v_2^II \quad (3)$$

$$i_1 = i_1^I \quad (4)$$

$$i_2 = i_2^II \quad (5)$$

$$i_3 = i_2^II. \quad (6)$$

Using (1)–(6), the following simple relationships may be found between the three-port  $z$ -parameters  $[Z]$  of the dual-gate MESFET (which may be derived from measured three-port  $S$ -parameters using the transformation in Appendix I) and the individual two-port  $z$ -parameters of the two single-gate FET's:

$$\begin{aligned} Z_{11} &= Z_{11}^I & Z_{12} &= Z_{12}^I & Z_{13} &= Z_{12}^I \\ Z_{21} &= Z_{21}^I & Z_{22} &= (Z_{22}^I + Z_{11}^I) & Z_{23} &= (Z_{22}^I + Z_{12}^I) \\ Z_{31} &= Z_{21}^I & Z_{32} &= (Z_{22}^I + Z_{21}^I) & Z_{33} &= (Z_{22}^I + Z_{22}^I). \end{aligned} \quad (7)$$

It can be seen readily from (7) that three of the four two-port  $z$ -parameters of FET1 ( $Z_{11}^I$ ,  $Z_{12}^I$ , and  $Z_{21}^I$ ) are given explicitly, and that the fourth parameter  $Z_{22}^I$  is added

to each of the four  $z$ -parameters of FET2. In order to complete the two-port description for FET1, an estimate of  $Z_{22}^I$  is required. An analysis of the  $z$ -parameter expressions for the single-gate FET model in Fig. 2(b) shows that up to moderate frequencies

$$Z_{12} \approx \frac{C_D}{C_G + C_D} Z_{22}.$$

This expression is accurate within 2-percent magnitude for frequencies to at least 6 GHz. Since  $C_D \ll C_G$ , this implies that  $Z_{12} \ll Z_{22}$ . Hence, assuming that  $Z_{12}^H \ll Z_{22}^I$ , then the estimate for  $Z_{22}^I$  can be formed from

$$Z_{22}^I \approx Z_{23}. \quad (8)$$

Equation (8) has been found to give reasonable accuracy for the overall determination of FET1 elements, especially since the other three  $z$ -parameters are obtained explicitly from the matrix in (7).

Inspection of (7) also shows that two estimates are available for both  $Z_{12}^I$  and  $Z_{21}^I$ . Ideally,  $Z_{21}^I = Z_{21} = Z_{31}$  and  $Z_{12}^I = Z_{12} = Z_{13}$ . In practice, the simplest means of accounting for errors in the measured three-port  $z$ -parameter data is to average the two available estimates; i.e.,  $Z_{21}^I = (Z_{21} + Z_{31})/2$  and  $Z_{12}^I = (Z_{12} + Z_{13})/2$ . A further improvement in accuracy is possible by choosing those relevant three-port  $z$ -parameters which are less sensitive to small errors in the measured  $S$ -parameters. Such a sensitivity analysis was carried out and indicated that  $\text{Re}(Z_{13})$ ,  $\text{Im}(Z_{12})$ , and  $\text{Im}(Z_{21})$  were slightly more robust in their insensitivity to small errors in the measured  $S$ -parameters. Hence, the following expressions are likely to yield the most accurate values for  $Z_{12}^I$  and  $Z_{21}^I$ :

$$\text{Re}(Z_{12}^I) = \text{Re}(Z_{13}) \quad (9)$$

$$\text{Im}(Z_{12}^I) = \text{Im}(Z_{12}) \quad (10)$$

$$\text{Re}(Z_{21}^I) = (\text{Re}(Z_{21}) + \text{Re}(Z_{31}))/2 \quad (11)$$

$$\text{Im}(Z_{21}^I) = \text{Im}(Z_{21}). \quad (12)$$

By using (7)–(12), the four  $z$ -parameters of FET1 may be determined directly from the three-port  $z$ -parameters of the dual-gate MESFET. The FET1  $z$ -parameters [ $Z^I$ ] may then be converted to  $y$ -parameters [ $Y^I$ ] by a matrix inversion, and these  $y$ -parameters then are used to calculate the FET1 model elements using the expressions in [12]. For convenience, these expressions are reproduced in Appendix II.

### B. FET2 Model Elements

A study of (7) shows that the two-port  $z$ -parameters of FET2 [ $Z^H$ ] appear in the three-port  $z$ -parameters with  $Z_{22}^I$  added to them. Hence, errors in the  $Z_{22}^I$  estimate from the three-port  $z$ -parameters cause a systematic error to propagate in all of the [ $Z^H$ ] elements. For example, the assumption that  $Z_{22}^I \approx Z_{23}$  means that the model for FET2 must be unilateral (since  $Z_{12}^H$  must be zero), which will degrade accuracy. Hence, a decomposition of the matrix in (7) to give [ $Z^H$ ] using an estimate for  $Z_{22}^I$  could not be used in the case of FET2 for accuracy reasons.

Instead, expressions were developed to determine the FET2 element values from measured three-port  $y$ -parameters of the device, together with the already evaluated FET1 elements. The general expressions for the three-port  $y$ -parameters of the model in Fig. 3 were derived, and it was found that the remaining 7 elements of FET2 could be evaluated, provided an estimate for the transconductance of FET2 ( $g_{m2}$ ) was available. This element may be determined quite simply from dc measurements using a new analytical dc model which has recently been published by one of the authors [13]. The method uses new closed-form expressions to calculate the internal voltages of the two single-gate FET parts from the external bias conditions on the complete dual-gate MESFET, and hence defines the operating state of each single-gate FET part. The transconductance of FET2 then may be determined using the following expression:

$$g_{m2} = \frac{\partial I_{D2}}{\partial V_{GS2}} \quad (13)$$

where  $I_{D2}$  and  $V_{GS2}$  are defined in Fig. 1(b).

The FET2 elements in terms of the FET1 elements  $g_{m2}$  and the three-port  $y$ -parameters may be obtained successively using the expressions presented below.

Assuming that

$$(1 + j\omega C_{G1} R_{11}) \approx 1 \quad (14)$$

and

$$(1 + j\omega C_{G2} R_{12}) \approx 1 \quad (15)$$

then

$$C_{G2} \approx \frac{1}{\omega} \text{Im} \left[ \frac{-g_{m2}}{1 + \frac{Y_{12}(y_{m1} - j\omega C_{D1})}{Y_{21}(j\omega C_{D1})}} \right] \quad (16)$$

$$g_{02} = \frac{1}{R_{02}} \approx -\omega C_{G2} \text{Im} \left[ \frac{Y_{31}}{Y_{21}} \right] - g_{m2} \quad (17)$$

$$C_{D2} \approx -\frac{\text{Im}[Y_{23}]}{\omega} - \frac{C_{G2} g_{02}}{g_{m2} + g_{01} + g_{02}} \quad (18)$$

$$C_{S2} \approx \text{Im} \left[ \frac{-(Y_{23} + j\omega C_{D2})(y_{m1} - j\omega C_{D1})}{\omega Y_{21}} \right] \quad (19)$$

where

$$y_{m1} = g_{m1} e^{-j\omega \tau_1}.$$

Also, if

$$C_{G2} \gg g_{m2} \tau_2$$

then

$$\tau_2 \approx -\frac{1}{\omega} \left\{ \arg \left( \frac{Y_{31}}{Y_{21}} \right) + \frac{\pi}{2} \right\}. \quad (20)$$

It has been found that, for a range of typical dual-gate MESFET parameters, the above approximations are valid for frequencies up to at least 6 GHz. The final element  $R_{12}$  was assumed to be equal to  $R_{11}$ . This assumption does not

affect the accuracy of the model very much, as its effect on the calculated  $S$ -parameters is fairly small. The transformation from three-port  $S$ -parameters to three-port  $y$ -parameters is presented in Appendix I.

#### IV. RESULTS

In order to test the performance of the present modeling procedure, measured three-port  $S$ -parameter data for a dual-gate MESFET as reported by Tsironis and Meierer [10] was used as a basis for comparison. The device (designated FET(a) in [10]) has gate 1 dimensions of  $0.8 \times 200 \mu\text{m}$ , gate 2 dimensions of  $2 \times 200 \mu\text{m}$ , an intergate spacing of  $2 \mu\text{m}$  and is biased with both FET parts in the saturation region.

Before commencing the modeling, the  $S$ -parameters were de-embedded back through the mounting parasitics so as to be referenced to the active device terminals. This requires characterization of parasitic elements such as bond wire inductances and test circuit interelectrode capacitances which are dependent upon the particular device mounting configuration used. One of the more important elements is the parasitic feedback capacitance between the first gate and the drain, which has an adverse effect on transistor performance [7]. Since there is a screening effect of the second gate on the device, the main contribution to this interelectrode capacitance usually comes from the test fixture [7]. This capacitance is accounted for as part of the embedding network, though in order to ensure it has a small effect on the parameters, a mounting configuration with low stray interelectrode coupling is desirable.

For best accuracy, measured  $S$ -parameter data for element evaluation of the model was taken in the 4–6-GHz range. (At lower frequencies, the sensitivity of the  $z$ -parameter and  $y$ -parameter transformations to errors in measured  $S$ -parameters increases, while at higher frequencies the assumptions in the analytical expressions for the model elements degrade.)

The results for the model elements obtained for the dual-gate MESFET are presented in Table I. The  $g_{m2}$  value used was derived from the value given by Tsironis and Meierer using [12, eq. (16)] because accurate dc information on the device was not available. Only three measured  $S$ -parameter data points were needed at 4, 5, and 6 GHz. The FET1 values obtained from this data was averaged, and these averaged values then were used to calculate the FET2 element values, which were averaged in turn.

An error function defined by

$$EF = \left\{ \sum_{f_k} \sum_{i,j} \frac{|S_{ij} \text{meas} - S_{ij} \text{calc}|^2}{\sum_{f_k} \sum_{i,j} |S_{ij} \text{meas}|^2} \right\}^{1/2},$$

$$k = 1, \dots, 10, (i, j) = (1, 2, 3) \quad (21)$$

(as used in [10], for comparison purposes) was evaluated for the  $S$ -parameters calculated with the element values given in Table I. The value of the error function  $EF$  was

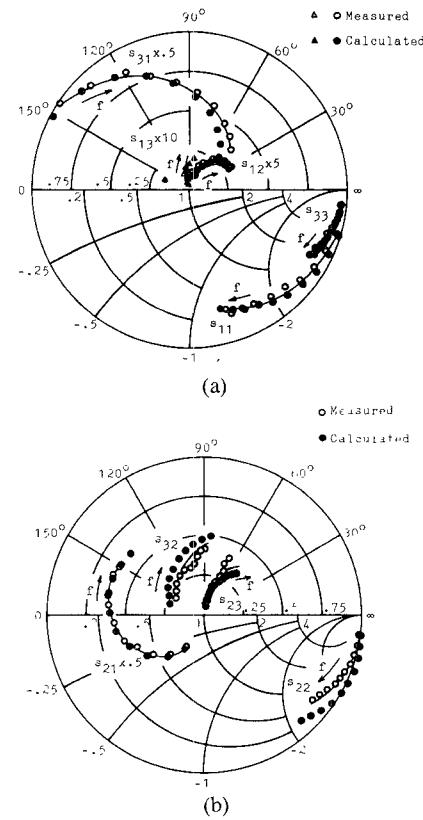

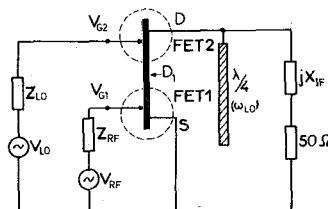

Fig. 5. Measured and calculated three-port  $S$ -parameters of the dual-gate MESFET with both FET parts in saturation.  $V_{DS} = 5\text{V}$ ,  $V_{GS1} = -1\text{V}$ ,  $V_{G2} = +2\text{V}$ ,  $I_D = 34\text{mA}$ . Port 1 = gate 1, port 2 = gate 2, port 3 = drain. Frequency: 2–11 GHz,  $\Delta F = 1 \text{GHz}$ .

TABLE I

EQUIVALENT CIRCUIT ELEMENT VALUES OF THE DUAL-GATE MESFET ( $i = 1, 2$ )

| Partial FET | $C_{D1}$      | $C_{G1}$         | $C_{S1}$      | $R_{O1}$    | $R_{I1}$   | $g_{m1}$        | $\tau_1$       |

|-------------|---------------|------------------|---------------|-------------|------------|-----------------|----------------|

| FET 1       | $20\text{fF}$ | $0.181\text{pF}$ | $51\text{fF}$ | $350\Omega$ | $17\Omega$ | $24.3\text{mS}$ | $0.7\text{ps}$ |

| FET 2       | $17\text{fF}$ | $0.288\text{pF}$ | $48\text{fF}$ | $400\Omega$ | $17\Omega$ | $15.0\text{mS}$ | $5.6\text{ps}$ |

9.8 percent over the frequency range of 2–11 GHz, which compares favorably with a value of  $EF \approx 8$  percent obtained using Tsironis and Meierer's equivalent circuit.

A plot of the measured and calculated three-port  $S$ -parameters of the dual-gate MESFET referenced to the active device terminals is given in Fig. 5(a) and (b). As expected from the value obtained for the error function, the agreement between the measured and calculated parameters is very good, although some small discrepancies do occur at the higher frequencies. These discrepancies may be due partially to the mounting parasitic element values used for de-embedding, or due to measurement errors arising from the microwave test fixture used [10] (eg., for  $S_{13}$  and  $S_{23}$ ).

If desired, the overall model accuracy can be improved further by employing a computer optimization on the

simplified model to minimize the error function EF. Since the model contains only 14 elements, and since the error function value without any optimization is low (9.8 percent), optimization towards a global minimum should proceed readily.

## V. CONCLUSIONS

A simplified model of the GaAs dual-gate MESFET has been developed where all of the parameters are determined from three-port *S*-parameter measurements over the 4–6 GHz frequency range, except for one transconductance element, which can be evaluated from dc data. The three-port *S*-parameters are measured with the transistor dc biased for normal operation, and no two-port *S*-parameter measurements under special bias conditions are required, which significantly reduces the number of RF measurements that need to be made. The method has been used to model a dual-gate MESFET where both FET parts are in saturation, and good agreement between measured and calculated *S*-parameters has been achieved over a multi-octave frequency range (2–11 GHz) without using computer optimization.

Due to its relative simplicity and ease of parameter acquisition, while maintaining good accuracy, the method should prove useful in circuit design and in the study of element value variation with dc bias, for large-signal modeling of the dual-gate MESFET.

## VI. ACKNOWLEDGMENT

Thanks are extended to D. F. Hewitt for discussions. Part of this work was performed while one of the authors, R. Minasian, was on study leave at the Laboratoires d'Electronique et de Physique Appliquée, France. The authors would gratefully like to acknowledge useful contributions made to this work by Dr. C. Tsironis and R. Meierer (from the above laboratory) through discussions, particularly regarding the *S*-parameter measurements.

## APPENDIX I

The following transformations for an *n*-port have been taken from [14]:

$$Z = Z_0(I + S)(I - S)^{-1} \quad (\text{AI1})$$

$$S = (Z - Z_0I)(Z + Z_0I)^{-1} \quad (\text{AI2})$$

$$Y = \frac{1}{Z_0}(I - S)(I + S)^{-1} \quad (\text{AI3})$$

$$S = (I - Z_0Y)(I + Z_0Y)^{-1} \quad (\text{AI4})$$

where

*S* network *S*-parameters,

*I* identity (unit) matrix,

*Z* network *z*-parameters,

*Y* network *y*-parameters, and

*Z*<sub>0</sub> characteristic impedance (normally 50Ω).

## APPENDIX II

The following expressions are reproduced from [12] for convenience, and applied to FET1.

Assuming  $(\omega R_{11}C_{G1})^2 \ll 1$ :

$$C_{D1} = \frac{-\text{Im}(Y_{12}^I)}{\omega} \quad (\text{AII1})$$

$$C_{S1} = \frac{\text{Im}(Y_{22}^I)}{\omega} - C_{D1} \quad (\text{AII2})$$

$$R_{01} = \frac{1}{\text{Re}(Y_{22}^I)} \quad (\text{AII3})$$

$$g_{m1} = \text{Re}(Y_{21}^I) \quad (\text{AII4})$$

$$C_{G1} = \frac{\text{Im}(Y_{11}^I)}{\omega} - C_{D1} \quad (\text{AII5})$$

$$R_{11} = \frac{\text{Re}(Y_{11}^I)}{(\omega C_{G1})^2} \quad (\text{AII6})$$

$$\tau_1 = \left\{ -\frac{\text{Im}(Y_{21}^I)}{\omega} - g_{m1}R_{11}C_{G1} - C_{D1} \right\} / g_{m1}. \quad (\text{AII7})$$

## REFERENCES

- [1] W. C. Tsai, S. F. Paik, and B. S. Hewitt, "Switching and frequency conversion using dual-gate FET's," in *Proc. 9th Eur. Microwave Conf.*, 1979, pp. 311–315.

- [2] C. Tsironis, R. Stahlmann, and F. Ponse, "A self-oscillating dual gate MESFET X-band mixer with 12dB conversion gain," in *Proc. 9th Eur. Microwave Conf.*, 1979, pp. 321–325.

- [3] C. A. Liechti, "Performance of dual-gate GaAs MESFET's as gain-controlled low-noise amplifiers and high-speed modulators," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-23, pp. 461–469, June 1975.

- [4] W. Filensky, F. Ponse, and H. Beneking, "Applications of dual-gate GaAs MESFET's for fast pulse shape regeneration systems," *Electron. Lett.*, vol. 16, pp. 214–216, March 13, 1980.

- [5] J. L. Vorhaus, R. A. Pucel, and Y. Tajima, "Monolithic dual-gate GaAs FET digital phase shifter," *IEEE Trans. Electron Devices*, vol. ED-29, pp. 1078–1088, July 1982.

- [6] G. Ohm and J. Czech, "12 GHz variable-gain amplifier with dual-gate GaAs FET for satellite use," in *Proc. 9th Eur. Microwave Conf.*, 1979, pp. 298–302.

- [7] S. Asai, F. Murai, and H. Kodera, "GaAs dual-gate Schottky-barrier FET's for microwave frequencies," *IEEE Trans. Electron Devices*, vol. ED-22, pp. 897–904, Oct. 1975.

- [8] T. Furutsuka, M. Ogawa, and N. Kawamura, "GaAs dual-gate MESFET's," *IEEE Trans. Electron Devices*, vol. ED-25, pp. 580–586, June 1978.

- [9] G. S. F. Mau, "Characterization and modeling of the dual-gate gallium arsenide field-effect transistor," M.Sc.E.E. thesis, Univ. of Santa Clara, 1981.

- [10] C. Tsironis and R. Meierer, "Microwave wide-band model of GaAs dual gate MESFET's," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 243–251, Mar. 1982.

- [11] H. Ashoka and R. S. Tucker, "S-parameter model of dual-gate GaAs MESFET," *Electron. Lett.*, vol. 19, pp. 39–40, Jan. 20, 1983.

- [12] R. A. Minasian, "Simplified GaAs MESFET model to 10 GHz," *Electron. Lett.*, vol. 13, pp. 549–551, Sept. 1, 1977.

- [13] R. A. Minasian, "Modelling DC characteristics of dual-gate GaAs MESFETs," *IEE Proc. Solid-State Electron.*, vol. 130, pp. 182–186, Aug. 1983.

- [14] K. C. Gupta, R. Garg, and R. Chadha, *Computer-Aided Design of Microwave Circuits*. Dedham, MA: Artech House, 1981, ch. 2, pp. 30–35.

**James R. Scott** (S'80) was born in Melbourne, Australia, in 1957. He received the B.Eng. (communication eng.) degree with distinction and the M.Eng. degree from the Royal Melbourne Institute of Technology in 1979 and 1982, respectively. In 1982 he was also awarded a COMSOC Scholarship by the IEEE Communications Society.

After completing the M.Eng. degree, he worked for a brief period with Consolidated Technology (Aust.) Pty. Ltd. on an X-band radar repeater and UHF oscillators. He then joined the Electrical Engineering Department at the University of Melbourne, where he is currently investigating the small and large signal operation of dual-gate GaAs FET's as the basis of a Ph.D. thesis.

His major research interests are in microwave active and passive circuits, the application of dual-gate FET's to optical communication systems, MIC fabrication techniques, and automated microwave measurement techniques.

**Robert A. Minasian** (S'78-M'80) was born in May, 1953. He received the B.E.(Elec.) degree from the University of Melbourne, Australia in 1974. In 1975, he was awarded a United Kingdom Commonwealth Scholarship, and received the M.Sc. degree with distinction from University College, University of London, in 1976. His Ph.D. studies involved research on the large signal operation of microwave MESFET transistors, and he was awarded the Ph.D. degree from the University of Melbourne in 1980. During 1983, he was a Visiting Research Fellow at the Laboratoires d'Electronique et de Physique Appliquée, France.

He is presently a Lecturer in Electrical Engineering at the University of Melbourne, Australia. His current research interests include microwave signal processing circuits, optoelectronic devices, and fiber optic communications.

Dr. Minasian is a senior member of the IREE.

## Dual-Gate MESFET Mixers

CHRISTOS TSIRONIS, MEMBER, IEEE, ROMAN MEIERER, AND RAINER STAHLMANN

**Abstract**—A theoretical and experimental investigation of dual-gate MESFET mixers is presented. Based on a detailed analysis of the different nonlinear modes of DGFET's, a computer-aided modeling procedure has been developed, which allowed to recognize and optimize critical circuit and bias conditions for high conversion gain and IF bandwidth. Theoretical results are in good agreement with experiments on a 12-GHz TV reception mixer with 8-dB conversion gain and 800-MHz bandwidth.

### I. INTRODUCTION

**I**N MODERN MICROWAVE superheterodyne receivers, GaAs FET's are used as preamplifiers, local oscillators, and mixers in hybrid [1] or monolithic [2] versions. Both single-gate FET's (SGFET's) and dual-gate FET's (DGFET's) are used as mixers, the last ones even up to *Ka*-band frequencies [3]. The advantages of employing DGFET's as down converters instead of Schottky diodes or SGFET's are, except for conversion gain and reasonable noise figure which are inherent also to SGFET mixers, the intrinsic separation of signal and local oscillator ports and the possibility of separate matching and direct combination of the corresponding powers inside the device. This avoids cumbersome passive couplers and is an important requirement of monolithic circuit designs. The MMIC's

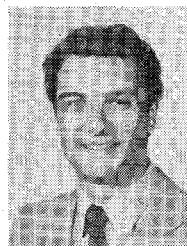

Fig. 1. Principle of DGFET mixer operation.

DGFET mixers are probably the only adequate solution, as has been shown in the case of *X*-band direct satellite broadcasting receivers [2].

In spite of the obvious importance of the mixer application of DGFET's, the mixing mechanism of this device is not yet completely understood. This is due to the floating potential of the intergate channel region ( $D_1$  in Fig. 1) strongly dependent on the amplitude of the local oscillator voltage applied onto either of the two gates. The bias and saturation conditions of both FET parts of the DGFET are consequently changing during LO voltage excursion and cause them to act as a mixer, or as RF resp. IF amplifier separately.

This paper deals with computer-aided modeling optimization and testing of DGFET mixers in the three principal mixing modes of practical interest. After an initial general investigation of mixing possibilities with DGFET's, the modeling procedure is described, and examples for two

Manuscript received June 14, 1983; revised December 5, 1983.

C. Tsironis and R. Meierer are with Laboratoires d'Electronique et de Physique Appliquée, 3 Avenue Descartes, 94450 Limeil-Brévannes, France.

R. Stahlmann is with the Institute of Semiconductor Electronics, Technical University of Aachen, West Germany.